# **Hardware Documentation**

# ADP-MIPI2LVDS1 for HW Revision 1.20

Version 004 (2021-07-26)

© F&S Elektronik Systeme GmbH Untere Waldplätze 23 D-70569 Stuttgart

Phone: +49(0)711-123722-0

Fax: +49(0)711-123722-99

### **About This Document**

This document describes how to use the ADP-MIPI2LVDS1 adapter board with mechanical and electrical information. The latest version of this document can be found at:

http://www.fs-net.de.

### **ESD Requirements**

All F&S hardware products are ESD (electrostatic sensitive devices). All products are handled and packaged according to ESD guidelines. Please do not handle or store ESD-sensitive material in ESD-unsafe environments. Negligent handling will harm the product and warranty claims become void.

### **History**

| Date       | ٧   | Platform | A,M,R | Chapter | Description                                                | Au |

|------------|-----|----------|-------|---------|------------------------------------------------------------|----|

| 26.11.2019 | 000 | All      |       | -       | Initial Version                                            | MD |

| 27.04.2020 | 001 | All      | Α     | 2       | Addition of the P/N numbers of connectors and mating parts | MD |

| 04.05.2020 | 002 | All      | М     | 5       | Update in chapter 5                                        | MD |

| 13.01.2021 | 003 | All      | A,M   | All     | New Hardware Version 1.10                                  | MD |

| 23.07.2021 | 004 | All      | M     | All     | Bugfixes and new Hardware Version 1.20                     | MD |

V Version

A, M, R Added, Modified, Removed

Au Author

# **Table of Contents**

| Abo  | out This Document          | 2  |

|------|----------------------------|----|

| ESE  | D Requirements             | 2  |

| Hist | tory                       | 2  |

| Tab  | ole of Contents            | 3  |

| 1    | Physical Characteristics   | 4  |

| 2    | Connector Layout           | 5  |

| 3    | Connector Pin Layouts      | 6  |

| 4    | Electrical Characteristics | 9  |

| 5    | ESD and EMI Implementation | 10 |

| 6    | Second source rules        | 10 |

| 7    | Storage conditions         | 10 |

| 8    | ROHS and REACH statement   | 10 |

| 9    | Packaging                  | 11 |

| 10   | Matrix Code Sticker        | 11 |

| 11   | Appendix                   | 12 |

|      | Important Notice           |    |

|      | Warranty Terms             | 13 |

| 12   | Content                    | 14 |

### **Physical Characteristics**

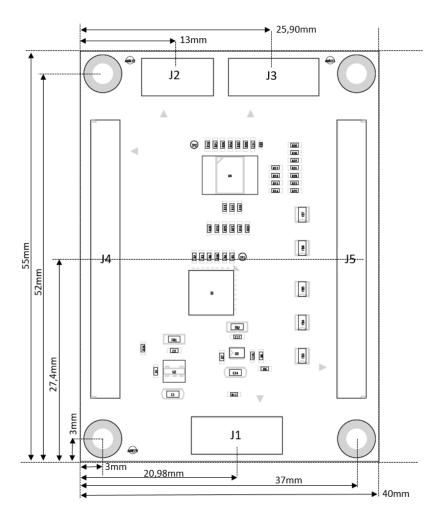

ADP-MIPI2LVDS1 is an adapter board that is able to convert MIPI-DSI signals into LVDS signals. The board can produce 2-channels of LVDS signals from one channel (4-data lanes) MIPI-DSI signal interface with the usage of Toshiba TC358775. The board can support up to WUXGA 1920 x 1200, 24-bit/pixel or QXGA 2048 x 1536, 18-bit/pixel panel resolutions.

Figure 1: ADP-MIPI2LVDS1 Adapter Board

| Dimensions                             | Description     |

|----------------------------------------|-----------------|

| Size                                   | 40mm x 55mm     |

| PCB Thickness                          | 1.66mm ± 0.16mm |

| Height of the parts on the top side    | 3.7mm           |

| Height of the parts on the bottom side | 0.5mm           |

| Weight                                 | N/A             |

Table 1: Mechanical Dimensions

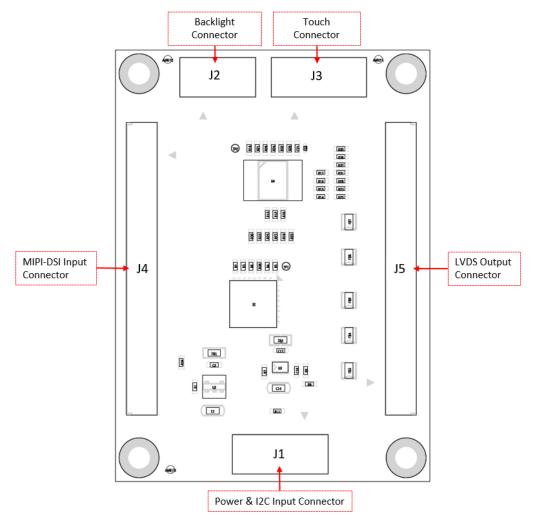

# 2 Connector Layout

Figure 2: Connector Layout

| Ref<br>• | Description                    | I/O    | No. of Pins | Connector Type      |

|----------|--------------------------------|--------|-------------|---------------------|

| J1       | Power and I2C Connector        | Input  | 6           | DF13-6P-1.25H(20)   |

| J2       | Backlight Connector            | Output | 4           | DF13-4P-1.25H(20)   |

| J3       | Touch Controller Connector     | Output | 6           | DF13-6P-1.25H(20)   |

| J4       | MIPI-DSI Connector             | Input  | 30          | FI-X30SSLA-HF-R2500 |

| J5       | LVDS Connector                 | Output | 30          | FI-X30SSLA-HF-R2500 |

|          | Mating Connector for J1 and J3 | -      | 6           | DF13-6S-1.25C       |

|          | Mating Connector for J2        | -      | 4           | DF13-4S-1.25C       |

|          | Mating Connector for J4 and J5 | -      | 30          | FI-X30H & FI-X30HL  |

Table 2: Connectors List and Types

# **3 Connector Pin Layouts**

| J4: MIPI-DSI Connector - Input |                 |     |         |                               |  |

|--------------------------------|-----------------|-----|---------|-------------------------------|--|

| Pin                            | Signal Name     | I/O | Voltage | Description                   |  |

| 1                              | MIPI_DSI _D0_N  | I   |         | MIPI-DSI Data Lane 0-         |  |

| 2                              | MIPI_DSI _D0_P  | I   |         | MIPI-DSI Data Lane 0+         |  |

| 3                              | MIPI_DSI _D1_N  | I   |         | MIPI-DSI Data Lane 1-         |  |

| 4                              | MIPI_DSI _D1_P  | I   |         | MIPI-DSI Data Lane 1+         |  |

| 5                              | MIPI_DSI _D0_N  | I   |         | MIPI-DSI Data Lane2-          |  |

| 6                              | MIPI_DSI _D0_P  | I   |         | MIPI-DSI Data Lane 2+         |  |

| 7                              |                 |     | GND     |                               |  |

| 8                              | MIPI_DSI _CLK_N | I   |         | MIPI-DSI Clock Signal-        |  |

| 9                              | MIPI_DSI _CLK_P | I   |         | MIPI-DSI Clock Signal+        |  |

| 10                             | MIPI_DSI _D3_N  | I   |         | MIPI-DSI Data Lane 3-         |  |

| 11                             | MIPI_DSI _D3_P  | I   |         | MIPI-DSI Data Lane 3+         |  |

| 12                             | N.C.            | X   | Х       | Not Connected                 |  |

| 13                             | N.C.            | Х   | X       | Not Connected                 |  |

| 14                             |                 |     | GND     |                               |  |

| 15                             | N.C.            | X   | X       | Not Connected                 |  |

| 16                             | N.C.            | Х   | X       | Not Connected                 |  |

| 17                             |                 |     | GND     |                               |  |

| 18                             | N.C.            | X   | X       | Not Connected                 |  |

| 19                             | N.C.            | X   | X       | Not Connected                 |  |

| 20                             | N.C.            | Х   | X       | Not Connected                 |  |

| 21                             | N.C.            | Χ   | X       | Not Connected                 |  |

| 22                             | N.C.            | X   | X       | Not Connected                 |  |

| 23                             | N.C.            | Χ   | X       | Not Connected                 |  |

| 24                             |                 |     | GND     |                               |  |

| 25                             | I2C_SDA         | I/O | 3.3V    | I2C Touch-Control Serial Data |  |

| 26                             | I2C_IRQn        | I   | 3.3V    | I2C Touch-Control Interrupt   |  |

| 27                             | I2C_SCL         | I   | 3.3V    | I2C Touch-Control Clock       |  |

| 28                             | MIPI_RSTn       | I   | 3.3V    | MIPI Reset Signal             |  |

| 29                             | VLCD            | PWR | 3.3V    | LCD Supply Voltage            |  |

| 30                             | VLCD            | PWR | 3.3V    | LCD Supply Voltage            |  |

Table 3: MIPI-DSI Connector Pin Layout

| J5: LVDS Connector - Output |                |     |         |                                   |  |

|-----------------------------|----------------|-----|---------|-----------------------------------|--|

| Pin                         | Signal Name    | I/O | Voltage | Description                       |  |

| 1                           | LVDS_A_DATAO_N | 0   | 1.2V    | LVDS A Data Lane 0-               |  |

| 2                           | LVDS_A_DATAO_P | 0   | 1.2V    | LVDS A Data Lane 0+               |  |

| 3                           | LVDS_A_DATA1_N | 0   | 1.2V    | LVDS A Data Lane 1-               |  |

| 4                           | LVDS_A_DATA1_P | 0   | 1.2V    | LVDS A Data Lane 1+               |  |

| 5                           | LVDS_A_DATA2_N | 0   | 1.2V    | LVDS A Data Lane2-                |  |

| 6                           | LVDS_A_DATA2_P | 0   | 1.2V    | LVDS A Data Lane 2+               |  |

| 7                           |                |     | GND     |                                   |  |

| 8                           | LVDS_A_CLK_N   | 0   | 1.2V    | LVDS A Clock Signal-              |  |

| 9                           | LVDS_A_CLK_P   | 0   | 1.2V    | LVDS A Clock Signal+              |  |

| 10                          | LVDS_A_DATA3_N | 0   | 1.2V    | LVDS A Data Lane 3-               |  |

| 11                          | LVDS_A_DATA3_P | 0   | 1.2V    | LVDS A Data Lane 3+               |  |

| 12                          | LVDS_B_DATAO_N | 0   | 1.2V    | LVDS B Data Lane 0-               |  |

| 13                          | LVDS_B_DATAO_P | 0   | 1.2V    | LVDS B Data Lane 0+               |  |

| 14                          |                |     | GND     |                                   |  |

| 15                          | LVDS_B_DATA1_N | 0   | 1.2V    | LVDS B Data Lane 1-               |  |

| 16                          | LVDS_B_DATA1_P | 0   | 1.2V    | LVDS B Data Lane 1+               |  |

| 17                          |                | 1   | GND     | '                                 |  |

| 18                          | LVDS_B_DATA2_N | 0   | 1.2V    | LVDS B Data Lane 2-               |  |

| 19                          | LVDS_B_DATA2_P | 0   | 1.2V    | LVDS B Data Lane 2+               |  |

| 20                          | LVDS_B_CLK_N   | 0   | 1.2V    | LVDS B Clock Signal-              |  |

| 21                          | LVDS_B_CLK_P   | 0   | 1.2V    | LVDS B Clock Signal+              |  |

| 22                          | LVDS_B_DATA3_N | 0   | 1.2V    | LVDS B Data Lane 3-               |  |

| 23                          | LVDS_B_DATA3_P | 0   | 1.2V    | LVDS B Data Lane 3+               |  |

| 24                          |                | 1   | GND     |                                   |  |

| 25                          | I2C_SDA        | I/O | 3.3V    | I2C Serial Data                   |  |

| 26                          | MIPI_INTn      | 0   | 3.3V    | MIPI Interrupt Signal             |  |

| 27                          | I2C_SCL        | 0   | 3.3V    | I2C Clock Signal                  |  |

| 28                          | MIPI_RSTn      | PWR | 3.3V    | MIPI Reset Signal (optional N.C.) |  |

| 29                          | VLCD           | PWR | 3.3V    | LCD Supply Voltage                |  |

| 30                          | VLCD           | PWR | 3.3V    | LCD Supply Voltage                |  |

Table 4: LVDS Connector Pin Layout

| J1:Power and I2C Connector - Input |             |     |         |                             |  |  |

|------------------------------------|-------------|-----|---------|-----------------------------|--|--|

| Pin                                | Signal Name | I/O | Voltage | Description                 |  |  |

| 1                                  | VDD_3V3     | PWR | 3.3V    | Voltage Power Supply        |  |  |

| 2                                  | I2C_SDA     | 1/0 | 3.3V    | I2C Serial Data             |  |  |

| 3                                  | I2C_SCL     | I   | 3.3V    | I2C Clock                   |  |  |

| 4                                  | TOUCH_RSTn  | ı   | 3.3V    | Touch Reset (optional N.C.) |  |  |

| 5                                  | I2C_INTn    | I   | 3.3V    | I2C Interrupt               |  |  |

| 6                                  | GND         |     |         |                             |  |  |

Table 5: Power and I2C Connector Pin Layout

| J2:Ba | J2:Backlight Connector - Output |     |         |                                  |  |  |  |

|-------|---------------------------------|-----|---------|----------------------------------|--|--|--|

| Pin   | Signal Name                     | I/O | Voltage | Description                      |  |  |  |

| 1     | N.C.                            | Х   | Х       | Not Connected                    |  |  |  |

| 2     | BL_ON                           | 0   | 3.3V    | Backlight On (Enable) -> Display |  |  |  |

| 3     | BL_PWM                          | 0   | 3.3V    | Backlight PWM -> Display         |  |  |  |

| 4     | GND                             |     |         |                                  |  |  |  |

Table 6: Power and I2C Connector Pin Layout

| J3:Touch Controller Connector - Output |                                              |     |         |                                 |  |  |

|----------------------------------------|----------------------------------------------|-----|---------|---------------------------------|--|--|

| Pin                                    | Signal Name                                  | I/O | Voltage | Description                     |  |  |

| 1                                      | VDD_3V3                                      | PWR | 3.3V    | Voltage Power Supply -> Display |  |  |

| 2                                      | I2C_SDA                                      | 1/0 | 3.3V    | I2C Serial Data -> Display      |  |  |

| 3                                      | I2C_SCL                                      | 0   | 3.3V    | I2C Clock -> Display            |  |  |

| 4                                      | TOUCH_RSTn                                   | 0   | 3.3V    | Touch Reset -> Display          |  |  |

| 5                                      | TOUCH_INTn O 3.3V Touch Interrupt -> Display |     |         |                                 |  |  |

| 6                                      | GND                                          |     |         |                                 |  |  |

Table 7: Power and I2C Connector Pin Layout

### 4 Electrical Characteristics

| Signal Name | Description          | Min | Тур. | Max | Unit |

|-------------|----------------------|-----|------|-----|------|

| VDD_3V3     | Input Supply Voltage | 3.0 | 3.3  | 3.6 | V    |

| VLCD        | LCD Supply Voltage   | 3.0 | 3.3  | 3.6 | V    |

| GND         | Ground               | -   | -    | -   | -    |

Table 8: Electrical Characteristics

#### 5 **ESD** and **EMI** Implementation

The LVDS data lanes were filtered via ferrite beads in order to reduce the EMI. We highly recommend using the adapter board with wires as short as possible.

ESD Rating of the chip is ±2 kV (HBM). The chip has limited built-in ESD protection. There is no ESD protection on the LVDS and MIPI-DSI connectors.

A helpful guide is available from TI; just search for slva680 at ti.com.

#### Second source rules 6

F&S qualifies their second sources for parts autonomously, as long as this does not touch the technical characteristics of the product. This is necessary to guarantee delivery times and product life. A setup of release samples with released second sources is not possible.

F&S does not use broker components without the consent of the customer.

#### Storage conditions 7

Maximum storage on room temperature with non-condensing humidity: Maximum storage on controlled conditions 25 ±5 °C, max. 60% humidity: 12 months For longer storage, we recommend vacuum dry packs.

#### ROHS and REACH statement 8

All F&S designs are created from lead-free components and are completely ROHS compliant.

The products we supply do not contain any substance on the latest candidate list published by the European Chemicals Agency according to Article 59(1,10) of Regulation (EC) 1907/2006 (REACH) in a concentration above 0.1 mass %.

Consequently, the obligations in No. 1 and 2 paragraphs in Annex are not relevant here. Please understand that F&S is not performing any chemical analysis on its products to testify REACH compliance and is therefore not able to fill out any detailed inquiry forms.

#### **Packaging** 9

All F&S ESD-sensitive products will shipping either in trays or in bags.

### 10 Matrix Code Sticker

All F&S hardware will ship with a matrix code sticker including the serial number. Enter your serial number here <a href="https://www.fs-net.de/en/support/serial-number-info-and-rma/">https://www.fs-net.de/en/support/serial-number-info-and-rma/</a> to get information on shipping date and type of board.

Figure 3: Matrix Code Sticker

### 11 Appendix

### **Important Notice**

The information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. F&S Elektronik Systeme ("F&S") assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained in this documentation.

F&S reserves the right to make changes in its products or product specifications or product documentation with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.

F&S makes no warranty or guarantee regarding the suitability of its products for any particular purpose, nor does F&S assume any liability arising out of the documentation or use of any product and specifically disclaims any and all liability, including without limitation any consequential or incidental damages.

Specific testing of all parameters of each device is not necessarily performed unless required by law or regulation.

Products are not designed, intended, or authorized for use as components in systems intended for applications intended to support or sustain life, or for any other application in which the failure of the product from F&S could create a situation where personal injury or death may occur. Should the Buyer purchase or use a F&S product for any such unintended or unauthorized application, the Buyer shall indemnify and hold F&S and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim of personal injury or death that may be associated with such unintended or unauthorized use, even if such claim alleges that F&S was negligent regarding the design or manufacture of said product.

Specifications are subject to change without notice.

### **Warranty Terms**

#### **Hardware Warranties**

F&S guarantees hardware products against defects in workmanship and material for a period of one (1) year from the date of shipment. Your sole remedy and F&S's sole liability shall be for F&S, at its sole discretion, to either repair or replace the defective hardware product at no charge or to refund the purchase price. Shipment costs in both directions are the responsibility of the customer. This warranty is void if the hardware product has been altered or damaged by accident, misuse or abuse.

#### **Software Warranties**

Software is provided "AS IS". F&S makes no warranties, either express or implied, with regard to the software object code or software source code either or with respect to any third party materials or intellectual property obtained from third parties. F&S makes no warranty that the software is useable or fit for any particular purpose. This warranty replaces all other warranties written or unwritten. F&S expressly disclaims any such warranties. In no case shall F&S be liable for any consequential damages.

#### **Disclaimer of Warranty**

THIS WARRANTY IS MADE IN PLACE OF ANY OTHER WARRANTY, WHETHER EXPRESSED, OR IMPLIED, OF MERCHANTABILITY, FITNESS FOR A SPECIFIC PURPOSE, NON-INFRINGEMENT OR THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION, EXCEPT THE WARRANTY EXPRESSLY STATED HEREIN. THE REMEDIES SET FORTH HEREIN SHALL BE THE SOLE AND EXCLUSIVE REMEDIES OF ANY PURCHASER WITH RESPECT TO ANY DEFECTIVE PRODUCT.

#### **Limitation on Liability**

UNDER NO CIRCUMSTANCES SHALL F&S BE LIABLE FOR ANY LOSS, DAMAGE OR EXPENSE SUFFERED OR INCURRED WITH RESPECT TO ANY DEFECTIVE PRODUCT. IN NO EVENT SHALL F&S BE LIABLE FOR ANY INCIDENTAL OR CONSEQUENTIAL DAMAGES THAT YOU MAY SUFFER DIRECTLY OR INDIRECTLY FROM USE OF ANY PRODUCT. BY ORDERING THE PRODUCT, THE CUSTOMER APPROVES THAT THE F&S PRODUCT, HARDWARE AND SOFTWARE, WAS THOROUGHLY TESTED AND HAS MET THE CUSTOMER'S REQUIREMETS AND SPECIFICATIONS

# 12 Content

| Table 1: Mechanical Dimensions              | 4 |

|---------------------------------------------|---|

| Table 2: Connectors List and Types          | 5 |

| Table 3: MIPI-DSI Connector Pin Layout      |   |

| Table 4: LVDS Connector Pin Layout          |   |

| Table 5: Power and I2C Connector Pin Layout |   |

| Table 6: Power and I2C Connector Pin Layout |   |

| Table 7: Power and I2C Connector Pin Layout |   |

| Table 8: Electrical Characteristics         |   |

| Figure 1: ADP-MIPI2LVDS1 Adapter Board      | 4 |

| Figure 2: Connector Layout                  | 5 |

| Figure 3: Matrix Code Sticker               |   |